Alat :

Battery dibutuhkan sebagai sumber daya energi agar rangkaian dapat bekerja.

IC

74151 merupakan salah satu dari sekian banyak kompenen multiplexer. IC

74151 memiliki 8 pin input dan juga mempunyai 3 selection dan ada pin

enabled. Pada pin output terdapat 2 pin yang memilik output berlawanan.

IC

74151 merupakan IC multiplekser yang memiliki satu buah data selektor

dengan delapan saluran masukan (D0 – D7) dan memiliki dua buah keluaran

(Y – W).

Pada tabel kebenaran dapat dilihat bahwa:

1. Jika pin Enable diberi logika HIGH, maka apapun masukan dan apapun keadaan pin Select maka keluaran akan selalu berlogika LOW.

2. Jika

pin Enable diberi logika LOW dan pin Select juga diberi logika LOW,

maka akan ada salah satu masukan yang di salurkan ke keluaran.

3. Keluaran pada pin W adalah kebalikan dari keluaran pin Y.

- IC 74150

IC

74150 merupakan IC multiplekser yang memiliki satu buah data selektor

dengan 16 saluran masukan (D0 – D15) dan memiliki satu saluran keluaran

(W).

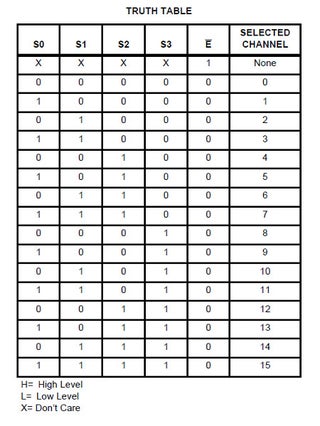

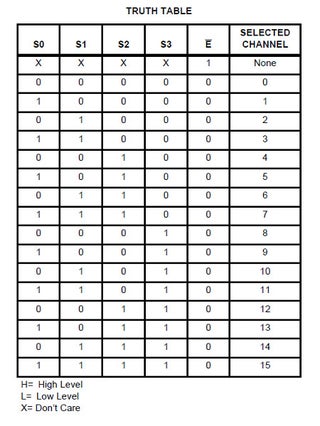

Pada tabel kebenaran dapat dilihat bahwa:

1. Jika pin Enable diberi logika HIGH, maka apapun masukan dan apapun keadaan pin Select maka keluaran akan selalu berlogika LOW.

2. Jika

pin Enable diberi logika LOW dan pin Select juga diberi logika LOW,

maka akan ada salah satu masukan yang di salurkan ke keluaran.

3. Logika keluaran pada pin W adalah kebalikan dari logika masukan.

Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan

hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter

(Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan

(kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin

mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau

Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan

dengan simbol minus (“-“) di atas Variabel Inputnya.

Gerbang logika AND ( IC 4081 )

Gerbang

AND (IC 4081) memerlukan 2 atau lebih Masukan (Input) untuk

menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan

Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1

dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari

masukan (Input) bernilai Logika 0.

Konfigurasi pin :

- Pin 7 adalah suplai negatif

- Pin 14 adalah suplai positif

- Pin 1 & 2, 5 & 6, 8 & 9, 12 & 13 adalah input gerbang

- Pin 3, 4, 10, 11 adalah keluaran gerbang

Spesifikasi :

- Catu daya : 3 V - 15 V

- Fungsi : Quad 2-Input AND Gate

- Propagation delay : 55 ns

- Level tegangan I/O : CMOS

- Kemasan : DIP 14-pin Gerbang Logika OR ( IC 4071)

OR

adalah suatu gerbang yang bertujuan untuk menghasilkan logika output

berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output

berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika

1.

Konfogurasi Pin :

Spesifikasi :

Tegangan Suplai: 5 hingga 7V

Tegangan Input: 5 hingga 7V

Kisaran suhu pengoperasian = -55 ° C hingga 125 ° C

Tersedia dalam paket SOIC 14-pin

4067

Resistor ini digunakan pada sebagai hambatan yang resistansinya ditentukan untuk tiap-tiap cabang.

alat yang digunakan untuk menganalisa logika keluaran (Boolean 1 atau 0) dari sirkuit digital.

Gerbang

Logika (Logic Gates) adalah sebuah entitas untuk melakukan pengolahan

input-input yang berupa bilangan biner (hanya terdapat 2 kode bilangan

biner yaitu, angka 1 dan 0) dengan menggunakan Teori Matematika Boolean

sehingga dihasilkan sebuah sinyal output yang dapat digunakan untuk

proses berikutnya.

Dalam bab sebelumnya, kami menjelaskan secara panjang lebar rangkaian logika kombinasional yang dapat digunakan untuk melakukan operasi aritmatika dan operasi terkait. Bab ini membahas yang lain secara komprehensif kelas blok bangunan yang digunakan untuk merancang sirkuit kombinasional yang lebih kompleks, dan mencakup bangunan blok seperti multiplexer dan demultiplexer dan perangkat turunan lainnya seperti encoder dan decoder. Penekanan khusus diberikan pada dasar-dasar operasional dan penggunaan perangkat ini untuk merancang lebih banyak rangkaian kombinasional yang kompleks. Informasi yang relevan dengan aplikasi dalam hal daftar yang umum digunakan sirkuit terpadu yang tersedia dalam kategori ini, bersama dengan deskripsi fungsionalnya diberikan untuk akhir bab. Teks telah diilustrasikan secara memadai dengan bantuan sejumlah besar contoh yang terpecahkan.

8.1 Multiplexer

Multiplexer atau MUX, juga disebut pemilih data, adalah rangkaian kombinasional dengan lebih dari satu jalur masukan, satu jalur keluaran dan lebih dari satu jalur pilihan. Ada beberapa IC multiplekser yang memberikan output yang saling melengkapi. Juga, multiplexer dalam bentuk IC hampir selalu memiliki ENABLE atau input STROBE, yang harus aktif agar multiplexer dapat melakukan fungsinya

fungsi. Multiplexer memilih informasi biner yang ada pada salah satu jalur input, tergantung pada status logika input seleksi, dan mengarahkannya ke jalur output. Jika ada n garis pilihan, maka jumlah jalur input maksimum yang mungkin adalah 2n dan multiplekser disebut sebagai 2n-ke-1 multiplexer atau 2n × 1 multiplexer. Gambar 8.1(a) dan (b) masing-masing menunjukkan representasi rangkaian dan tabel kebenaran multiplexer 4-ke-1 dasar.

Untuk membiasakan pembaca dengan perangkat multiplexer praktis yang tersedia dalam bentuk IC, Gambar 8.2 dan 8.3 masing-masing menunjukkan representasi rangkaian dan tabel fungsi multiplekser 8-ke-1 dan 16-ke-1. Itu Multiplexer 8-ke-1 pada Gambar 8.2 adalah tipe IC nomor 74151 dari keluarga TTL. Ini memiliki RENDAH aktif AKTIFKAN masukan dan berikan keluaran pelengkap. Gambar 8.3 mengacu pada tipe IC nomor 74150 dari keluarga TTL. Ini adalah multiplexer 16-ke-1 dengan input LOW ENABLE aktif dan output LOW aktif.

8.1.1 Di dalam Multiplexer

Kami akan menjelaskan secara singkat jenis rangkaian logika kombinasional yang ditemukan di dalam multiplekser dengan: mempertimbangkan multiplekser 2-ke-1 pada Gambar. 8.4(a), tabel fungsionalnya ditunjukkan pada Gambar. 8.4(b). Gambar 8.4(c) menunjukkan kemungkinan diagram logika dari multiplexer ini. Rangkaian tersebut berfungsi sebagai berikut:

1. Untuk S = 0, ekspresi Boolean untuk output menjadi Y = I0.

2. Untuk S = 1, ekspresi Boolean untuk output menjadi Y = I1.

Jadi, input I0 dan I1 masing-masing dialihkan ke output untuk S = 0 dan S = 1. Memperpanjang konsep lebih lanjut, Gambar. 8.5 menunjukkan diagram logika multiplexer 4-ke-1. Kombinasi masukan 00, 01, 10 dan 11 pada jalur pilih masing-masing mengalihkan I0, I1, I2 dan I3 ke output. Pengoperasian sirkuit diatur oleh fungsi Boolean (8.1). Demikian pula, multiplexer 8-ke-1 dapat direpresentasikan oleh fungsi Boolean (8.2):

Seperti diuraikan sebelumnya, multiplexer biasanya memiliki input ENABLE yang dapat digunakan untuk mengontrol fungsi multipleks. Ketika input ini diaktifkan, yaitu saat berada dalam status logika '1' atau logika '0', tergantung pada apakah input ENABLE masing-masing aktif HIGH atau aktif LOW, output diaktifkan. Multiplexer berfungsi normal. Ketika input ENABLE tidak aktif, outputnya adalah

dinonaktifkan dan secara permanen beralih ke status logika '0' atau logika '1', tergantung pada apakah outputnya tidak dilengkapi atau dilengkapi. Gambar 8.6 menunjukkan bagaimana multiplexer 2-ke-1 pada Gambar 8.4 dapat dimodifikasi untuk memasukkan input ENABLE. Tabel fungsional multiplexer yang dimodifikasi ini juga ditunjukkan pada Gambar. 8.6. Input AKTIFKAN di sini aktif saat TINGGI. Beberapa paket IC memiliki lebih dari satu multiplekser. Dalam hal ini, input ENABLE dan input seleksi adalah umum untuk semua multiplexer dalam paket IC yang sama. Gambar 8.7 menunjukkan multiplexer 4-ke-1 dengan aktif LOW ENABLE memasukkan.

8.1.2 Menerapkan Fungsi Boolean dengan Multiplexer

Salah satu aplikasi multiplexer yang paling umum adalah penggunaannya untuk implementasi kombinasional fungsi logika Boolean. Teknik paling sederhana untuk melakukannya adalah dengan menerapkan MUX 2n-ke-1 untuk mengimplementasikan fungsi Boolean variabel-n. Baris input yang sesuai dengan masing-masing minterm yang ada di Fungsi Boolean dibuat sama dengan keadaan logika '1'. Minterm tersisa yang tidak ada di Fungsi Boolean dinonaktifkan dengan membuat jalur input yang sesuai sama dengan logika '0'. sebagai contoh, Gambar 8.8(a) menunjukkan penggunaan MUX 8-ke-1 untuk mengimplementasikan fungsi Boolean yang diberikan dengan persamaan

Dalam hal variabel A, B dan C, persamaan (8.3) dapat ditulis sebagai berikut:

Seperti yang ditunjukkan pada Gambar. 8.8, jalur input yang sesuai dengan tiga minterm yang ada dalam Boolean yang diberikan fungsi terikat dengan logika '1'. Lima kemungkinan minterm tersisa yang tidak ada dalam fungsi Boolean adalah terikat dengan logika '0'. Namun, ada teknik yang lebih baik yang tersedia untuk melakukan hal yang sama. Dalam hal ini, MUX 2n-ke-1 dapat menjadi digunakan untuk mengimplementasikan fungsi Boolean dengan n + 1 variabel. Prosedurnya adalah sebagai berikut.

Dari n +1 variabel, n terhubung ke n garis seleksi multiplexer 2n-ke-1. Variabel yang tersisa digunakan dengan jalur input. Berbagai jalur input terikat ke salah satu dari berikut ini: '0', '1', yang tersisa variabel dan komplemen dari variabel sisa. Baris mana yang diberikan status logika apa mudah ditentukan dengan bantuan prosedur sederhana. Prosedur lengkap diilustrasikan untuk Fungsi boolean diberikan oleh persamaan (8.3). Ini adalah fungsi Boolean tiga variabel. Secara konvensional, kita perlu menggunakan multiplexer 8-ke-1 untuk mengimplementasikan fungsi ini. Sekarang kita akan melihat bagaimana ini dapat diimplementasikan dengan multiplexer 4-ke-1. Multiplexer yang dipilih memiliki dua jalur seleksi. Langkah pertama di sini adalah menentukan tabel kebenaran dari fungsi Boolean yang diberikan, yang ditunjukkan pada Tabel 8.1.

Pada langkah selanjutnya, dua dari tiga variabel dihubungkan ke dua garis seleksi, dengan urutan yang lebih tinggi variabel yang terhubung ke garis seleksi tingkat tinggi. Misalnya, dalam kasus ini, variabel

B dan C adalah variabel yang dipilih untuk garis seleksi dan masing-masing terhubung ke seleksi garis S1 dan S0. Pada langkah ketiga, tabel dari jenis yang ditunjukkan pada Tabel 8.2 dibangun. Di bawah input ke multiplexer, minterms terdaftar dalam dua baris, seperti yang ditunjukkan. Baris pertama mencantumkan istilah-istilah di mana variabel A yang tersisa dilengkapi, dan baris kedua mencantumkan suku-suku di mana A tidak dilengkapi.

Ini mudah dilakukan dengan bantuan tabel kebenaran. Minterm yang diperlukan diidentifikasi atau ditandai dengan cara tertentu dalam tabel ini. Dalam diberikan tabel, entri ini telah disorot. Setiap kolom diperiksa satu per satu. Jika tidak ada minterm kolom tertentu disorot, '0' ditulis di bawahnya. Jika keduanya disorot, '1' adalah

tertulis. Jika hanya satu yang disorot, variabel terkait (dilengkapi atau tidak dilengkapi) ditulis. Jalur input kemudian diberikan status logika yang sesuai. Dalam kasus ini, I0, I1, I2 dan I3 masing-masing akan terhubung ke A, 0, A dan A. Gambar 8.8(b) menunjukkan logikanya penerapan.

Tidak perlu memilih hanya variabel paling kiri dalam urutan yang akan digunakan sebagai input ke

multiplekser. Variabel mana pun dapat digunakan asalkan tabel implementasi dibuat demikian. Dalam masalah yang diilustrasikan di atas, A dipilih sebagai variabel untuk jalur input, dan karenanya baris pertama dari tabel implementasi berisi entri-entri di mana 'A' berada dilengkapi dan baris kedua berisi entri-entri di mana A tidak dilengkapi. Jika kita menganggap C sebagai variabel yang ditinggalkan, tabel implementasi akan seperti yang ditunjukkan pada Tabel 8.3.

Gambar 8.9 menunjukkan implementasi perangkat keras. Untuk kasus B menjadi variabel kiri, tabel implementasi ditunjukkan pada Tabel 8.4 dan implementasi perangkat keras ditunjukkan pada Gambar 8.10.

8.1.3 Multiplexer untuk Konversi Data Paralel-ke-Serial

Meskipun data diproses secara paralel di banyak sistem digital untuk mencapai kecepatan pemrosesan yang lebih cepat, ketika datang untuk mentransmisikan data ini dengan jarak yang relatif jauh, ini dilakukan secara serial. Paralel pengaturan dalam hal ini sangat tidak diinginkan karena akan membutuhkan sejumlah besar transmisi garis. Multiplexer mungkin dapat digunakan untuk konversi paralel ke serial. Gambar 8.11 menunjukkan salah satunya pengaturan di mana multiplexer 8-ke-1 digunakan untuk mengubah data biner paralel delapan-bit menjadi serial membentuk. Sebuah counter tiga bit mengontrol input seleksi. Saat penghitung melewati 000 hingga 111, keluaran multiplexer melewati I0 hingga I7. Proses konversi membutuhkan total delapan siklus clock. Di dalam pada gambar yang ditunjukkan, pencacah tiga bit telah dibangun dengan bantuan tiga flip-flop sakelar.

Berbagai rangkaian counter dari berbagai jenis dan kompleksitas, bagaimanapun, tersedia dalam bentuk IC. Flip-flop dan counter dibahas secara rinci dalam Bab 10 dan 11.

Example 8.1

Terapkan fungsi produk jumlah Boolean yang dinyatakan oleh 1,2,5 oleh multiplekser yang sesuai.?

Solusi:

• Misalkan fungsi Boolean adalah f (A B C) = phi 1, 2, 5.

• Ekspresi jumlah hasil kali ekuivalen dapat ditulis sebagai f (A B C)= sigma 0, 3, 4, 6, 7.

Tabel kebenaran untuk fungsi Boolean yang diberikan diberikan pada Tabel 8.5. Fungsi yang diberikan dapat berupa diimplementasikan dengan multiplexer 4-ke-1 dengan dua jalur seleksi. Variabel A dan B dipilih untuk garis seleksi. Tabel implementasi seperti yang digambar dengan bantuan tabel kebenaran diberikan pada Tabel 8.6. Gambar 8.12 menunjukkan implementasi perangkat keras.

Example 8.2

Gambar 8.13 menunjukkan penggunaan multiplexer 8-ke-1 untuk mengimplementasikan Boolean empat variabel tertentu fungsi. Dari susunan rangkaian logika yang diberikan, turunkan ekspresi Boolean yang diimplementasikan oleh sirkuit yang diberikan.

Solusi

Masalah ini dapat diselesaikan dengan hanya bekerja mundur dalam prosedur yang diuraikan sebelumnya untuk merancang rangkaian logika berbasis multiplexer untuk fungsi Boolean yang diberikan. Di sini, implementasi perangkat keras diketahui dan tujuannya adalah untuk menentukan ekspresi Boolean yang sesuai.

Dari rangkaian logika yang diberikan, kita dapat menggambar tabel implementasi seperti yang diberikan pada Tabel 8.7. Itu baris pertama (0, 1, 2, 3, 4, 5, 6, 7) dan baris kedua (8, 9, 10, 11, 12, 13, 14, 15) adalah jadi karena variabel seleksi yang dipilih untuk diterapkan pada input adalah variabel MSB D. Entri di baris pertama termasuk semua minterms yang berisi D, dan entri di baris kedua termasuk semua minterm yang mengandung D. Setelah menulis entri di dua baris pertama, entri di baris ketiga baris dapat diisi dengan memeriksa status logika dari jalur input yang berbeda dalam rangkaian logika yang diberikan diagram. Setelah menyelesaikan baris ketiga, entri yang relevan di baris pertama dan kedua disorot. Ekspresi Boolean sekarang dapat ditulis sebagai berikut

8.1.4 Sirkuit Multiplexer Cascading

Mungkin ada situasi di mana jumlah saluran input yang diinginkan tidak tersedia di IC multiplexer. Sejumlah perangkat dengan ukuran tertentu dapat digunakan untuk membangun multiplexer yang dapat menangani sejumlah besar saluran input. Misalnya, multiplexer 8-ke-1 dapat digunakan untuk membangun Sirkuit multiplexer 16-ke-1 atau 32-ke-1 atau bahkan lebih besar. Langkah-langkah dasar yang harus diikuti untuk melaksanakan desain adalah sebagai berikut:

1. Jika 2n adalah jumlah jalur input pada multiplexer yang tersedia dan 2N adalah jumlah jalur input pada multiplexer yang diinginkan, maka jumlah multiplexer individu yang diperlukan untuk membangun yang diinginkan rangkaian multiplexer akan menjadi 2N−n.

2. Dari pengetahuan tentang jumlah input seleksi dari multiplexer yang tersedia dan dari multiplexer yang diinginkan, hubungkan bit yang kurang signifikan dari input pemilihan multiplexer yang diinginkan ke input pemilihan multiplexer yang tersedia.

3. Bit yang tersisa dari input seleksi dari rangkaian multiplexer yang diinginkan digunakan untuk mengaktifkan atau nonaktifkan multiplekser individu sehingga keluarannya ketika ORed menghasilkan keluaran akhir. Itu prosedur diilustrasikan dalam contoh yang diselesaikan 8.3.

Example 8.3

Rancang multiplexer 16-ke-1 menggunakan dua multiplexer 8-ke-1 yang memiliki input aktif LOW ENABLE

Solusi

Multiplexer 16-ke-1 dapat dibangun dari dua multiplexer 8-ke-1 yang memiliki ENABLE memasukkan. Input ENABLE diambil sebagai variabel pilihan keempat yang menempati posisi MSB.

Gambar 8.14 menunjukkan diagram rangkaian logika lengkap. IC 74151 dapat digunakan untuk mengimplementasikan 8-to-1 multiplekser.

Rangkaian tersebut berfungsi sebagai berikut. Ketika S3 dalam keadaan logika '0', multiplexer atas diaktifkan dan multiplexer yang lebih rendah dinonaktifkan. Jika kita mengingat tabel kebenaran dari fungsi Boolean empat variabel, S3 akan menjadi '0' untuk delapan entri pertama dan '1' untuk delapan entri lainnya. Oleh karena itu, ketika S3 = 0 output akhir akan menjadi salah satu input dari D0 ke D7, tergantung pada status logika S2, S1 dan S0. Begitu pula saat S3 = 1 output akhir akan menjadi salah satu input dari D8 ke D15, sekali lagi tergantung pada status logika S2, S1 dan S0. Oleh karena itu, rangkaian mengimplementasikan tabel kebenaran dari 16-ke-1 multiplekser.

1. Siapkan semua alat dan bahan yang diperlukan

2. Cari komonen yang diperlukan di library proteus

3. Untuk rangkaian multiplexer, memiliki 4 buah rangkaian dengan alat dan bahannya yaitu multiplexer ic 74150, INVERTER, led, gerbang logika OR, gerbang logika AND, logicprobe dan logic state, jk flip-flop

4. Atur nilai logic state

5. Coba dijalankan rangkaian

Gambar rangkaian 8.4

Representasi sirkuit multiplexer 2-ke-1

Gambar rangkaian 8.5

Diagram logika multiplexer 4-ke-1.

Gambar rangkaian 8.6

Multiplexer 2-ke-1 dengan input ENABLE.

Gambar rangkaian 8.7

Multiplexer 4-ke-1 dengan input ENABLE.

Prinsip Kerja:

Pada

gambar-gambar di atas merupakan jenis-jenis dari IC multiplexer mulai

dari 2x1, 4x1, dan 8x1. Berikut juga dengan bagaimana rangkaian di

dalamnya, yaitu menggunakan gerbang logika AND dan OR. Pada gambar 8.11

juga digunakan flip-flop sebagai rangkaian (Multiplexer for

parallel-to-serial conversion).

Multiplexer

adalah suatu perangkat yang dapat menerima beberapa input data dan

hanya satu diantara input yang akan dilewat ke output pada suatu waktu.

Pada gambar 8.1 contohnya digunakan mux 4x1 yang memiliki selector S0

dan S1. Jika ingin meloloskan input I0 maka selector S0 dan S1 harus 0.

Jika ingin Meloloskan input I1 maka selector S0= 1 sedangkan S1= 0.

Namun jika ingin meloloskan I2, maka S1=1 dan S0= 0. Saat ingin

meloloskan I3, maka kedua selector harus aktif HIGH.

.png)

.png)

.png)

.png)

.png)